# **GD** CONTROL DATA CORPORATION

**CDC**°

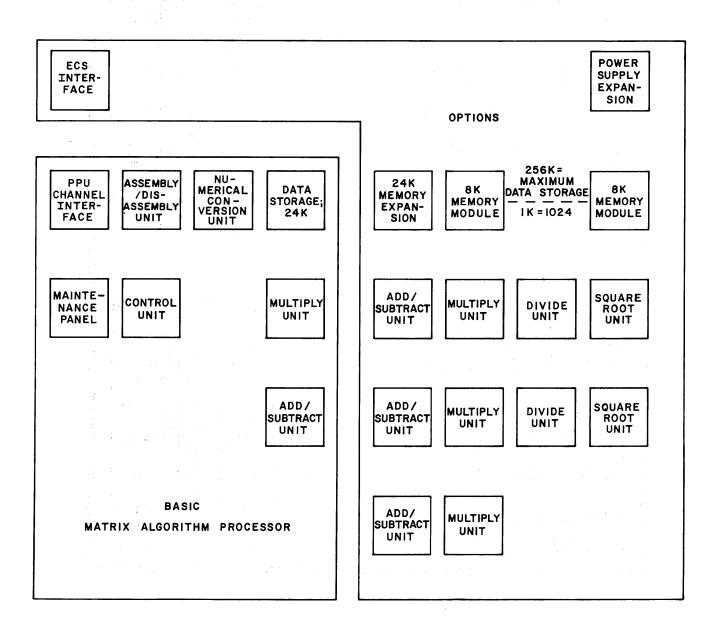

**AE121-B** MATRIX ALGORITHM PROCESSOR

**AE125-B** MATRIX ALGORITHM PROCESSOR

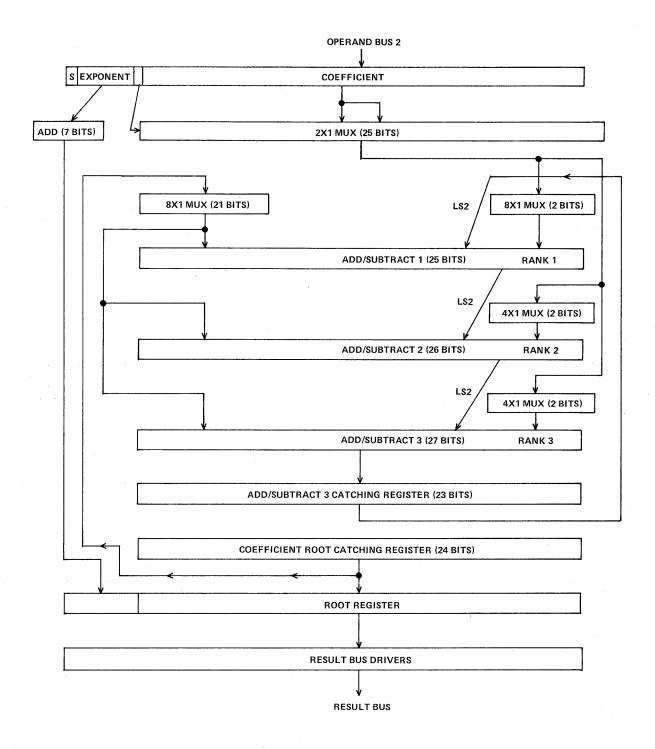

AT304-A SQUARE ROOT UNIT

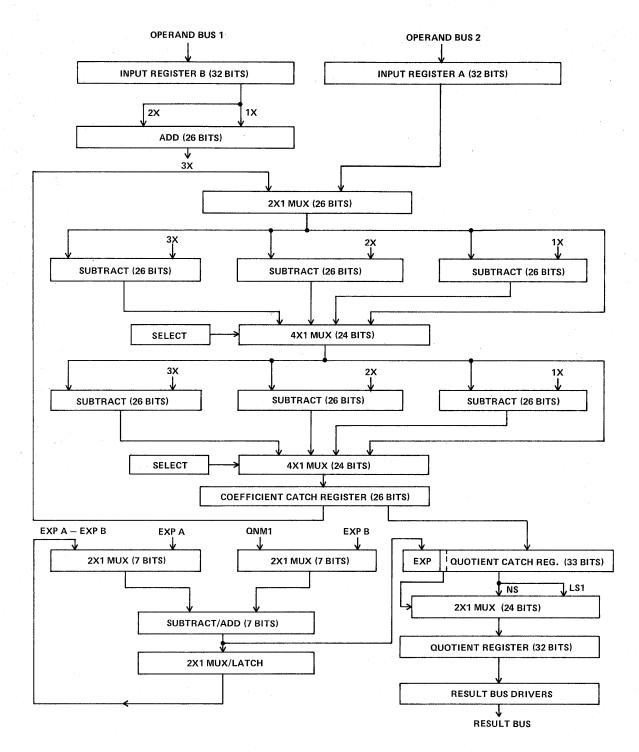

AT305-A DIVIDE UNIT

AT306-A ADD/SUBTRACT UNIT

AT307-A MULTIPLY UNIT

AT397-A ENHANCED-FFT ADD/SUBTRACT UNIT

AT400-A FFT ENHANCEMENT

BB318-A 8K MEMORY MODULE

BB320-A 24K MEMORY EXPANSION

**GD803-A POWER SUPPLY EXPANSION**

GENERAL DESCRIPTION OPERATION AND PROGRAMMING THEORY OF OPERATION

Volume 1 of 3

HARDWARE MAINTENANCE MANUAL

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| REVISION RECORD  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| REVISION         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| A                | Manual released.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| (10-15-76)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| В                | Manual revised; includes Field Change Order 38344. Pages iii, iv, 2-1, 2-2, 2-37 in volume 1;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| (12-15-77)       | iii, iv, 4-2, sheet PWR of section 5 in volume 2; iii, iv, 8-48, and 8-49 in volume 3 are revised.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| С                | Manual revised; includes Engineering Change Order 37207 and Field Change Order 37233. Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| (3-31-78)        | iii, iv in volume 1; iii, iv, sheets PPL, PPM, ADD1 3.1, ADD1 3.2, ADD2 3.1, A/D2 3.7,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|                  | BUS 3.1, BUS 3.4, CHN1 3.1, CHN1 3.5, CT7 3.6, CT7 3.10, CT9 3.4, ECS1 3.1, ECS1 3.4,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                  | ECS1 3.7, MUL1 3.3 in volume 2; and pages iii, iv, and 8-13 in volume 3 are revised.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| D .              | Manual revised; includes Publications Change Order 39518. Front cover, title page, iv, v,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| (10-24-78)       | 2-31 in volume 1; front cover, title page, iv, v, sheet MAP 1.5 in volume 2; front cover, title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| المراز المعاليين | page, iv, v, and 8-33 in volume 3 are revised. Pages ADD1 3.1A, sheet ADD1 3.1A,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| er er er         | ADD2 3.1A, sheet ADD2 3.1A, ADD2 3.2A, and sheet ADD2 3.2A in volume 2; and 8-34 in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                  | volume 3 are added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  | William Committee on the Committee of th |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| **               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| * * *            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  | and the second of the second o |  |  |  |  |  |  |  |

REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1976, 1977, 1978 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation Publications and Graphics Division 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

# MANUAL TO EQUIPMENT LEVEL CORRELATION SHEET

| SHEET_1       | _of_2_     | EQUIPMENTS |             |         |         |         |         |

|---------------|------------|------------|-------------|---------|---------|---------|---------|

| MANUAL<br>REV | FCO OR ECO | AE121-B    | AT304-A     | AT305-A | AT306-A | AT307-A | BB318-A |

| A             | Released   | B01        | A01         | A01     | A01     | A01     | A01     |

| В             | FCO38344   | B02        | <b>A</b> 01 | A01     | A01     | A01     | A01     |

| С             | ECO37207   | B03        | A01         | A01     | A 01    | A01     | A01     |

|               | FCO37233   | B04        | A01         | A 01    | A 02    | A02     | A01     |

|               |            |            |             |         |         |         |         |

|               |            |            |             |         |         |         |         |

|               |            |            |             |         |         |         |         |

|               |            |            |             |         |         |         |         |

|               |            |            |             |         |         |         |         |

| :             |            |            | ;           |         |         |         |         |

|               |            | ,          |             |         |         |         |         |

|               |            |            |             |         | ,       |         |         |

|               |            |            |             |         | ·       |         |         |

|               |            |            |             |         |         |         |         |

|               |            |            |             |         |         |         |         |

|               |            |            | !           |         |         |         |         |

|               |            |            |             |         |         |         |         |

|               |            |            |             |         |         |         | ,       |

|               |            |            |             |         | 1       |         |         |

|               |            |            |             |         |         |         |         |

|               |            |            |             |         |         |         | ·       |

|               | ·          |            |             |         | ·       |         |         |

|               |            |            |             |         |         |         |         |

|               |            |            |             |         |         |         |         |

|               | L          |            |             |         |         |         |         |

# MANUAL TO EQUIPMENT LEVEL CORRELATION SHEET (Cont'd)

| SHEET 2       | _OF_2_     | EQUIPMENTS |         |            |          |          |   |

|---------------|------------|------------|---------|------------|----------|----------|---|

| MANUAL<br>REV | FCO OR ECO | BB320-A    | GD803-A | AE125-B    | A T397-A | AT400-A  |   |

| A             | Released   | A01.       | A01     | -          | •        | <b>_</b> |   |

| В             | FCO38344   | A01        | A01     | -          | _        | -        | · |

| С             | ECO37207   | A 02       | A01     | <b>-</b> . | _        | -        |   |

|               | FCO37233   | A 02       | A01     | <b>-</b>   | -        | -        |   |

| D             | ECO39518   | -          | -       | B01        | A01      | A01      |   |

|               |            |            |         |            |          |          |   |

|               |            |            |         |            |          | ,        |   |

|               |            |            |         |            |          |          |   |

|               |            |            |         |            |          |          |   |

# **PREFACE**

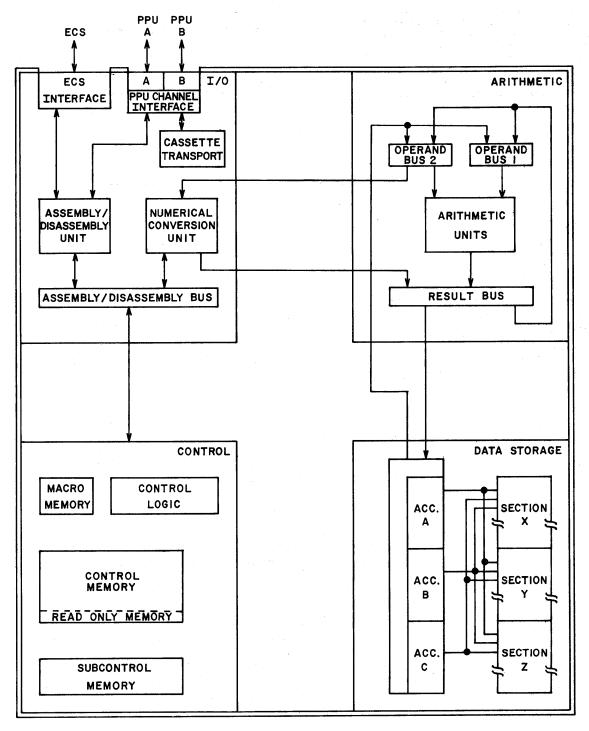

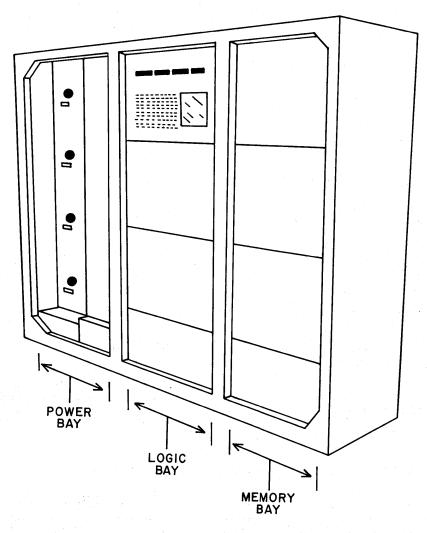

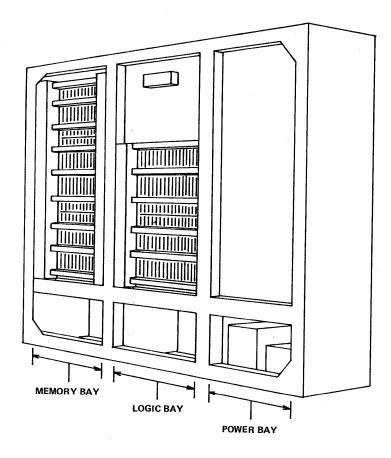

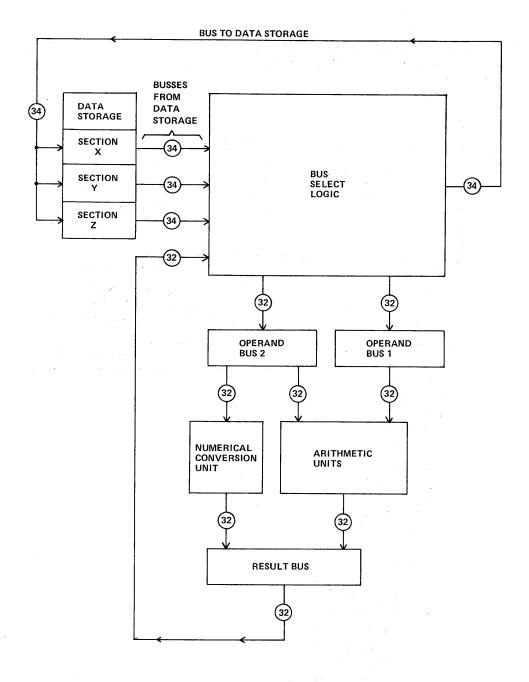

This manual provides hardware maintenance information for the CDC® AE121-B/AE125-B Matrix Algorithm Processor (MAP) and its related options. Volume 1 of the manual contains equipment descriptions, hardware reference information, and operational theory. Volume 2 contains installation procedures, diagrams, and maintenance information. Volume 3 contains parts data and wire lists.

One of the components of MAP is the NCR M63-2-STD cassette transport. NCR manual MS-413 provides training and field service information for this transport.

The MAP hardware maintenance manual is intended for use mainly by customer engineers. The following table defines the user and purpose of supplementary and related documents. Control Data assumes no responsibility for the contents of the uncontrolled documents listed in the table.

# NOTES